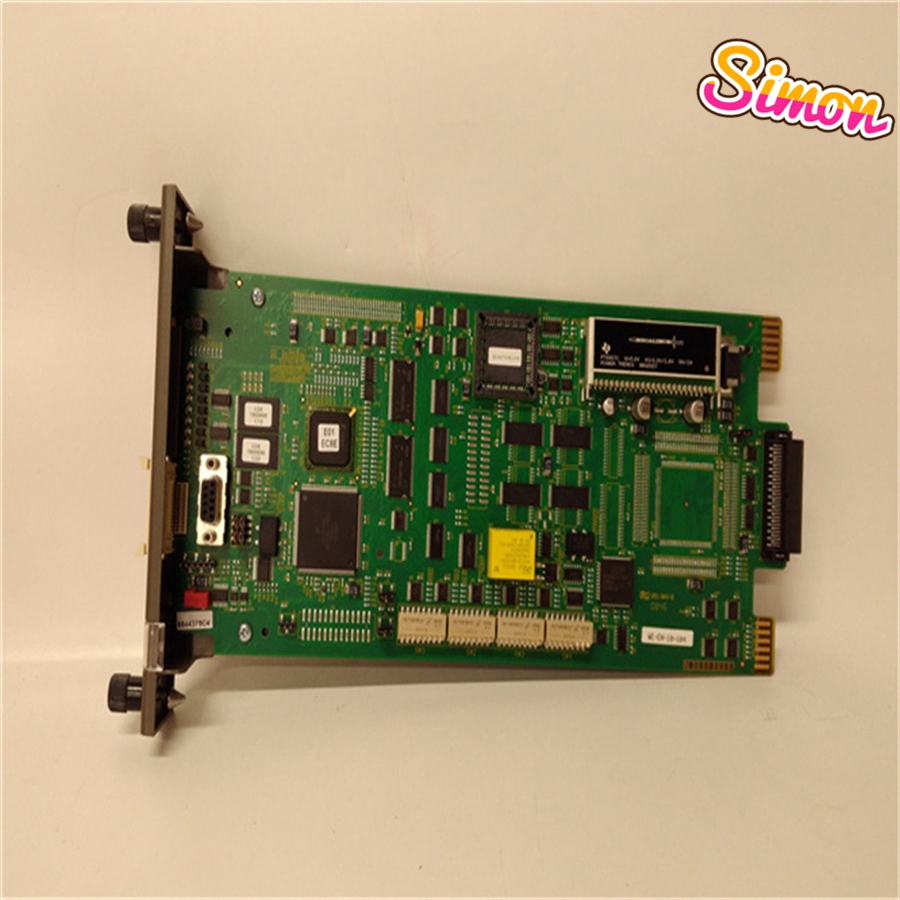

BAILEY INIIT13 高信号频率到达 ADC 来避免混叠

BAILEY INIIT13 高信号频率到达 ADC 来避免混叠

从这些说明性示例中可以看出,混叠的令人不安的本质是它会导致 ADC 报告完全不正确但完全合理的信号。避免混叠的唯一方法是确保采样率比信号周期快得多:这里的一个好的规则是每个周期至少采样 10 次,以获得感兴趣的最高信号频率。

如果我们不能将 ADC 的采样率设置为明显快于我们可能遇到的最高信号频率,我们可以通过阻止那些高信号频率到达 ADC 来避免混叠。这可以通过在 ADC 输入之前放置一个模拟低通滤波器电路来实现。这种“前端”电路称为抗混叠滤波器:

但是,如果系统的一部分以太慢的速率“采样”另一部分的数字输出,数字系统中仍可能出现混叠。这方面的一个例子可能是数字控制系统(如 DCS)轮询由数字传感器网络(如无线电连接过程变送器网络或数字现场总线变送器网络)收集的过程变量值的速率。如果 DCS 轮询速率与数字发射器报告的信号频率相比足够慢,则可能会导致混叠。防止这种潜在问题的最好办法是在整个系统中同步采样率,或者(或者)确保数据源始终以比读取它们的任何函数都慢得多的速率输出值。请记住,实际(最小)采样率与信号周期之比为 10:

SACE750090R0002

R1.SW2/3

R1.CAIR

CSA464AE

HIEE400106R0001

UAC326AE

HIEE401481R0001

NU8976A

HIER466665R99/NU8976A99

LT8978bV1

HIEE320639R0001

ARC093AV1

HIEE300690R1

UAC318AE

HIEE300744R1

UFC092BE01

UNS2980c-ZV4

HIEE205019R4

AFC094AE02

HIEE200130R0002

UNS0874A

HIER471062P1

咨询:BAILEY INIIT13 高信号频率到达 ADC 来避免混叠